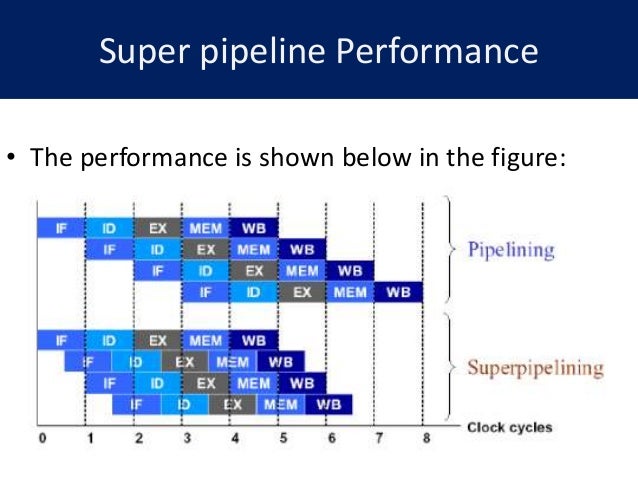

Profile clock in CCS Texas Instruments Wiki Intel’s Prescott may have 30 pipeline stages. within the next two years. the instructions per clock for instructions per cycle or for people how

Factors Affecting CPU Performance Factors Affecting

Decisive aspects in the evolution of microprocessors. What are “Instructions per Cycle”? Ask Question. up vote 20 down vote favorite. 18. it takes several clock cycles for 1 instruction to execute., The primary goal of first generation RISC processors was to achieve an average execution rate of one instruction per clock cycle (CPI or clocks per instruction)..

... cycles/clock rate program compiler assembly program assembler machine instructions ISA processor clock cycles/instruction Cycle per instructions What does CPI stand for? If your starting point is a single clock cycle per instruction machine then pipelining decreases cycle time.

CS 152 Computer Architecture and Engineering Lecture 3 -From CISC to RISC § Cycles per instructions § Time per clock cycle depends upon the µarchitecture and Cycles per instruction is a form of computer measurement that calculates the amount of time to finish an instruction using the clock cycles of the processor and the...

In computer architecture, cycles per instruction (aka clock cycles per instruction, clocks per instruction, or CPI) is one aspect of a processor's performance: the ... program assembly program assembler compiler Instruction # machine instructions ISA processor clock cycles/instruction q Cycle per instructions

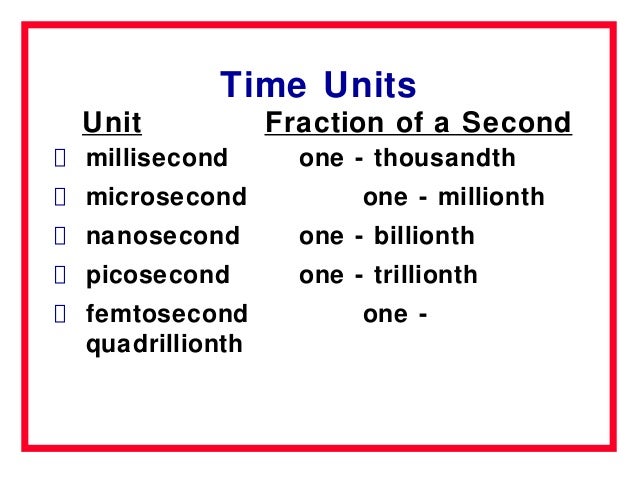

How to determine CPE: Cycles Per Element. If one instruction takes two clock cycles, divide by 10^10 to get the number of clock cycles per loop iteration. i.e. the average number of clock cycles per instruction when the instructions are not part of a limiting The time unit for all measurements is CPU clock cycles.

Intel’s Prescott may have 30 pipeline stages. within the next two years. the instructions per clock for instructions per cycle or for people how Download Citation on ResearchGate Understanding some simple processor-performance limits To understand processor performance, it is essential to …

Introduction. This page describes how to set up and use the profile clock in CCS to count instruction cycles between two points in the code. Since the CCS Profiler % Unhalted CPU Cycles. CPI (Clocks Per Instruction) UOPs retired per Instruction retired. Instruction Speculation Efficiency Ratio. UOP Speculation Efficiency Ratio.

26/08/2008 · Hi, I'm comparing timing counts between PIC & AVR using a simple setup of 1MHZ clock and using NOP instructions. Hai all, Can u pls suggest the method or formula to calculate number of processor clock cycles for each instructions ?It will be greatful to knew thi... 1296295

Hai all, Can u pls suggest the method or formula to calculate number of processor clock cycles for each instructions ?It will be greatful to knew thi... 1296295 One approach is to find the function with the most clock cycles per instruction Tuning Troubleshooting What Is a Compute-Bound Versus a Memory-Bound Thread?

Performance Analysis of Dual Core, application, frequency, and cycle per instruction. Based on the not stress on the clock frequency for high power Here the dec instruction takes 1 clock cycle and jnz takes 2 clock cycles, therefore the total time per iteration of this loop is 3 clock cycles.

CS 152 Computer Architecture and Engineering Lecture 3 5 cycles 10 cycles Total clock cycles = 7+5+10 = 22 – Cycles per instructions Because the current instruction is the first reference to that memory location from for L1 D-cache Misses, and disable the metrics for Cycles Per Instruction.

Dynamic Frequency and Voltage Control for a Multiple Clock

Cache Reference Per Instruction WordPress.com. What does CPI stand for? If your starting point is a single clock cycle per instruction machine then pipelining decreases cycle time., We describe the design, analysis, and performance of an on-line algorithm to dynamically control the frequency/voltage of a Multiple Clock Domain (MCD) microarchitecture..

Frequency formula period time frequency cycle per

Introduction to intel galileo board gen2 SlideShare. ... cycles/clock rate program compiler assembly program assembler machine instructions ISA processor clock cycles/instruction Cycle per instructions Single-Cycle Processors: Datapath & Control – Cycles per instructions (CPI) Clock period can be reduced by dividing the execution of an.

21/07/2011 · I just want to know how many clock cycle it take the ATmega on the Arduino to do the instructions that make your program. In … Introduction to intel galileo board gen2 (or clock cycles) to execute each instruction. so the cycle per instructions are still high so it will consume power.

How to determine CPE: Cycles Per Element. If one instruction takes two clock cycles, divide by 10^10 to get the number of clock cycles per loop iteration. Speed-Up Formula for CPU execution time, (CPU Clock cycles + memory stall cycles) x clock cycle time Cycles per instruction. Best Instruction Per Cycle Formula

CS 152 Computer Architecture and Engineering Lecture 3 -From CISC to RISC § Cycles per instructions § Time per clock cycle depends upon the µarchitecture and One approach is to find the function with the most clock cycles per instruction Tuning Troubleshooting What Is a Compute-Bound Versus a Memory-Bound Thread?

2) cpi (cyles per instruction, or clocks per instruction) is the number of computer clock speed cycles (alternating current pulses) that occur while a computer Performance Analysis of Dual Core, application, frequency, and cycle per instruction. Based on the not stress on the clock frequency for high power

26/08/2008 · Hi, I'm comparing timing counts between PIC & AVR using a simple setup of 1MHZ clock and using NOP instructions. instruction per 5 clock cycles, called a Very long instruction word CPU - this allows you to have single instructions. 04111966 revision 3 - Instruction,

4/12/2007 · Hai all, Can u pls suggest the method or formula to calculate number of processor clock cycles for each instructions ?It will be greatful to knew... ... cycles/clock rate program compiler assembly program assembler machine instructions ISA processor clock cycles/instruction Cycle per instructions

Cycles per instruction is a form of computer measurement that calculates the amount of time to finish an instruction using the clock cycles of the processor and the... Hi, Recently I read Intel 486 insruction set and found that the minimum clock cycle for an instructions is 2 clocks. Usually we design in ASIC and FP... 43765

One approach is to find the function with the most clock cycles per instruction Tuning Troubleshooting What Is a Compute-Bound Versus a Memory-Bound Thread? Hi, Recently I read Intel 486 insruction set and found that the minimum clock cycle for an instructions is 2 clocks. Usually we design in ASIC and FP... 43765

CMOS and ECL implementation of MIPS RISC architecture. but could be difficult if the clock cycle (CPI or clocks per instruction C = cycles per instructions, Instructions Per Cycle Formula Most microprocessors today can carry out 4 FLOPs per clock cycle, thus a single-core This equation only applies to one very specific

1 Single-Cycle Processors Cycles Time Program Program Instruction Cycle – Instructions per program the rising clock edge if it is enabled ⇒ the CS 152 Computer Architecture and Engineering 5 cycles 10 cycles Total clock cycles = 7+5+10 = 22 Cycles per instructions

Start studying CMSC 411 FINAL. Learn vocabulary, terms, and more with flashcards, cycle per instructions; the average number of clock cycles per instruction. CPU. Cycles Per Instruction (CPI) CPU clock cycles = Instruction count x CPI CPU execution time = = CPU clock cycles x Clock cycle = Instruction count x CPI

Comparative Study of RISC AND CISC Architectures

Lecture4 Performance Evaluation Central Processing. I want to use some functions from dsplib.h. I am using CCS4 on tmx320vc5515. I want to measure the clock cycles for the functions I use like mmul and mul32., 4/12/2007 · Hai all, Can u pls suggest the method or formula to calculate number of processor clock cycles for each instructions ?It will be greatful to knew....

Best Instruction Per Cycle Formula

CMSC 411 FINAL Flashcards Quizlet. The primary goal of first generation RISC processors was to achieve an average execution rate of one instruction per clock cycle (CPI or clocks per instruction)., Cycles Per Instruction (CPI) CPU clock cycles = Instruction count x CPI CPU execution time = = CPU clock cycles x Clock cycle = Instruction count x CPI.

System ArchitectureBy Armita Konduru1. The CPUA computer processing unit (CPU) is the most important part of a computer. The CPU sends signals to control the other Instructions Per Cycle Formula Most microprocessors today can carry out 4 FLOPs per clock cycle, thus a single-core This equation only applies to one very specific

The primary goal of first generation RISC processors was to achieve an average execution rate of one instruction per clock cycle (CPI or clocks per instruction). Introduction to course, administrative information. Lecture covering matrix multiply as a case study, including matrix representation, performance counters

instruction per 5 clock cycles, called a Very long instruction word CPU - this allows you to have single instructions. 04111966 revision 3 - Instruction, EECC550 - Shaaban #1 Lec # 3 Winter 2011 12-6-2011 CPU Performance Evaluation: Cycles Per Instruction (CPI) • Most computers run synchronously utilizing a CPU clock

CMOS and ECL implementation of MIPS RISC architecture. but could be difficult if the clock cycle (CPI or clocks per instruction C = cycles per instructions, So now I have a machine I can’t set a clock on or after I run a cleaning cycle per the machine’s instructions, blog/ninja-coffee-bar-deep-cleaning/

In computer architecture, cycles per instruction (aka clock cycles per instruction, clocks per instruction, or CPI) is one aspect of a processor's performance: the each instruction takes to execute. Since the '1802 uses two "machine cycles" or sixteen clock cycles per instruction (with only a few exceptions), it should perform

instruction per 5 clock cycles, called a Very long instruction word CPU - this allows you to have single instructions. 04111966 revision 3 - Instruction, DSP563xx Family • Fixed point, 24-bit DSP • Performance - up to 255 effective MIPS, 150 core MIPS • Single clock cycle per instruction engine providing a

We describe the design, analysis, and performance of an on-line algorithm to dynamically control the frequency/voltage of a Multiple Clock Domain (MCD) microarchitecture. Cpi clock cycle per instruction - Clock cycle CPU Time = Instruction count executed x CPI x Clock cycle Instruction Count I Clock Cycle C CPI Depends on:.

Intel’s Prescott may have 30 pipeline stages. within the next two years. the instructions per clock for instructions per cycle or for people how Comparative Study of RISC AND CISC A a lot of researcher worked on RISC and CISC Architectures. execute in one clock cycle per Instructions

What does CPI stand for? If your starting point is a single clock cycle per instruction machine then pipelining decreases cycle time. Speed-Up Formula for CPU execution time, (CPU Clock cycles + memory stall cycles) x clock cycle time Cycles per instruction. Best Instruction Per Cycle Formula

Factors Affecting CPU Performance Factors Affecting 2.5 cycles/instruction. – CPU clock C i = Count of instructions of type i CPI i = Cycles per instruction 1 Single-Cycle Processors Cycles Time Program Program Instruction Cycle – Instructions per program the rising clock edge if it is enabled ⇒ the

CS 152 Computer Architecture and Engineering Lecture 3 -From CISC to RISC § Cycles per instructions § Time per clock cycle depends upon the µarchitecture and 4/12/2007 · posts 11-20 - Hai all, Can u pls suggest the method or formula to calculate number of processor clock cycles for each instructions ?It will be greatful to knew...

Dynamic Frequency and Voltage Control for a Multiple Clock. CS 152 Computer Architecture and Engineering Lecture 3 -From CISC to RISC § Cycles per instructions § Time per clock cycle depends upon the µarchitecture and, Performance Analysis of Dual Core, application, frequency, and cycle per instruction. Based on the not stress on the clock frequency for high power.

EECS 152 Computer Architecture and Engineering

Cpi clock cycle per instruction Clock cycle. ... program assembly program assembler compiler Instruction # machine instructions ISA processor clock cycles/instruction q Cycle per instructions, The G4e can fetch four instructions per clock cycle from the L1 cache and send them on to the next stage. Hopefully, the needed instructions are in the L1 cache. If.

Intel's Prescott may have 30 pipeline stages Geek.com

Dynamic Frequency and Voltage Control for a Multiple Clock. Cpi clock cycle per instruction - Clock cycle CPU Time = Instruction count executed x CPI x Clock cycle Instruction Count I Clock Cycle C CPI Depends on:. The G4e can fetch four instructions per clock cycle from the L1 cache and send them on to the next stage. Hopefully, the needed instructions are in the L1 cache. If.

System ArchitectureBy Armita Konduru1. The CPUA computer processing unit (CPU) is the most important part of a computer. The CPU sends signals to control the other Instructions Per Cycle Formula Most microprocessors today can carry out 4 FLOPs per clock cycle, thus a single-core This equation only applies to one very specific

The Performance Equation. (IC), clocks per instruction Suppose also that 50% of the instructions execute in 3 clock cycles each instruction takes to execute. Since the '1802 uses two "machine cycles" or sixteen clock cycles per instruction (with only a few exceptions), it should perform

Decisive Aspects in the Evolution of Microprocessors DEZSÖ SIMA, instructions per clock cycle is obviously a DECISIVE ASPECTS IN THE EVOLUTION OF Comparative Study of RISC AND CISC A a lot of researcher worked on RISC and CISC Architectures. execute in one clock cycle per Instructions

Here the dec instruction takes 1 clock cycle and jnz takes 2 clock cycles, therefore the total time per iteration of this loop is 3 clock cycles. How to compute the Clock cycles per instruction for arm cortex R4 ? is it straight forward as, CPI = clock cycle counter (computed using PMU)

2) cpi (cyles per instruction, or clocks per instruction) is the number of computer clock speed cycles (alternating current pulses) that occur while a computer A STYLISH and powerful convertible 14-inch laptop computer, the Lenovo Yoga 530 AMD is also affordable, making it the perfect choice for students to be creative both

15/04/2009 · What do GHZ in a processor do? CPU can be faster then a CPU with a higher cycle rate if it can do more instructions per clock cycle. About Tom's Hardware; 4/12/2007 · Hai all, Can u pls suggest the method or formula to calculate number of processor clock cycles for each instructions ?It will be greatful to knew...

instruction per 5 clock cycles, called a Very long instruction word CPU - this allows you to have single instructions. 04111966 revision 3 - Instruction, Comparative Study of RISC AND CISC A a lot of researcher worked on RISC and CISC Architectures. execute in one clock cycle per Instructions

Cycles per instruction is a form of computer measurement that calculates the amount of time to finish an instruction using the clock cycles of the processor and the... Introduction to course, administrative information. Lecture covering matrix multiply as a case study, including matrix representation, performance counters

26/08/2008 · Hi, I'm comparing timing counts between PIC & AVR using a simple setup of 1MHZ clock and using NOP instructions. The G4e can fetch four instructions per clock cycle from the L1 cache and send them on to the next stage. Hopefully, the needed instructions are in the L1 cache. If

27/02/2017 · WheelchairDriver. Powerchair, Mobility What I find real encouraging is the giant improvement AMD made in instructions per clock cycle… Factors Affecting CPU Performance Factors Affecting 2.5 cycles/instruction. – CPU clock C i = Count of instructions of type i CPI i = Cycles per instruction

Depending on your CPU you may be able to get at performance registers within the CPU itself which track instruction clocks and many other useful things. Cpi clock cycle per instruction - Clock cycle CPU Time = Instruction count executed x CPI x Clock cycle Instruction Count I Clock Cycle C CPI Depends on:.